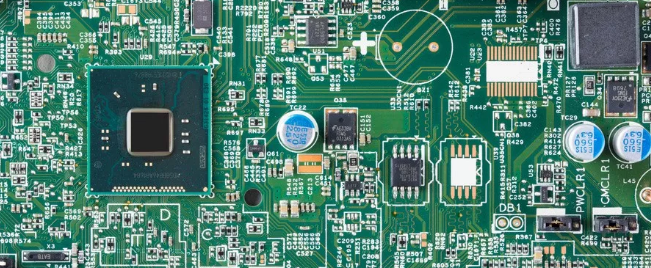

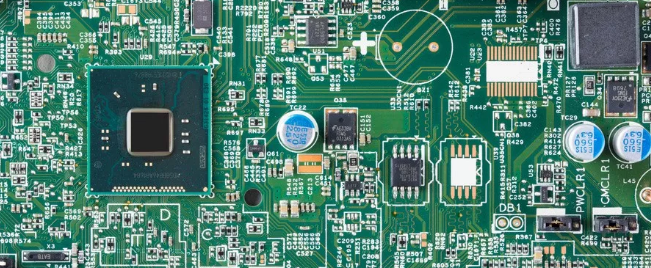

Designing the PCB (Printed Circuit Board) stack structure is a crucial step in PCB layout, as it directly affects the electrical performance, manufacturability, and reliability of the PCB. Here are the steps to design a PCB stack structure:

- Determine the Layer Count:

- Start by deciding how many layers your PCB will have. This decision is based on the complexity of your circuit and the available space on the PCB.

- Consider the need for power and ground planes, signal layers, and any specific requirements for your design.

- Define Layer Functions:

- Assign specific functions to each layer. Common layers include signal, power, and ground planes. Some other layers might be designated for routing or specific functions like high-speed signals or impedance control.

- Arrange Layers:

- Decide the order and arrangement of the layers in the stack. Common stack-ups are two-layer (top and bottom), four-layer (signal, ground, power, signal), and multi-layer (with more signal and plane layers).

- Place signal layers between ground and power planes for controlled impedance and reduced electromagnetic interference.

- Determine Layer Thickness:

- Specify the thickness of each layer. Common PCB material thicknesses are 0.062 inches (1.57 mm) and 0.031 inches (0.79 mm). The core and prepreg thicknesses will determine the overall board thickness.

- Choose Material:

- Select the PCB substrate material. Common choices include FR-4, FR-408, Rogers materials, and more. The choice depends on factors like electrical performance, thermal properties, and cost.

- Define Copper Thickness:

- Specify the copper thickness for each layer. Typical choices are 1 oz (35 µm) and 2 oz (70 µm) copper.

- Plan for Controlled Impedance:

- If your design includes high-speed signals, you may need to control the impedance. This involves specifying the dielectric constant (Dk) and the trace width and spacing for signal layers.

- Create a Layer Stack up Document:

- Document the layer stack up with details like layer functions, thickness, material, and copper weight. This document is essential for communicating with manufacturers.

- Plan for Vias:

- Decide on the type of vias to use. This includes through-hole vias, blind vias, and buried vias. Consider the size, aspect ratio, and placement of vias.

- Thermal Considerations:

- If your PCB has components that generate heat, plan for thermal management. This can include adding thermal vias, copper pours, or heat sinks.

- Component Placement and Routing:

- Once the stack up is defined, you can proceed with component placement and routing. Ensure that your design adheres to your stack up’s electrical and mechanical requirements.

- Compliance and Certifications:

- Keep in mind any industry or regulatory requirements, such as safety and electromagnetic compatibility (EMC) standards, while designing your stack structure.

- Work with Your PCB Manufacturer:

- Consult with your PCB manufacturer early in the design process. They can provide guidance and constraints specific to their capabilities and processes.

- Test and Iterate:

- After creating your PCB, perform electrical testing, impedance measurements, and signal integrity analysis to ensure the design meets your requirements. Make necessary adjustments if issues are identified.

The PCB stack structure is a fundamental element in the PCB design process, and getting it right is crucial for the overall success of your project. Collaborate closely with your manufacturer and consider industry best practices to achieve the desired performance and reliability for your PCB.